1.3.2. Aufbau eines Computers#

Grundbausteine#

Die Bausteine moderner Computer beruhen auf Halbleiterelementen, welche die CMOS-Technik (Complementary metal-oxide-semiconductor) verwenden. Aus den damit realisierten Transistoren können Spannungen (5 V bzw. 0 V) zur Schaltung von Zuständen geschaffen werden und damit logische Operationen in Form von Logikgattern gebaut werden. Die Weiterentwicklung der Fertigungstechnik ermöglicht eine kontinuierliche Verkleinerung der physikalischen Größe dieser Elemente, so dass die Dichte dieser Elemente immer weiter zunimmt.

Transistoren#

Die grundlegenden Recheneinheiten zum Rechnen mit binären Zahlen sind die logischen Gatter. Sie realisieren die logischen Operationen, z.B. das logische UND, ODER und NICHT, in Form von sogenannten Logikgattern. Das dafür notwendige elektrische Bauteil ist der Transistor, welcher den allergrößten Teil des datenverarbeitenden Teils eines Computers ausmacht.

Beispielhaft ist hier der Schaltplan eines UND-Gatters als Schaltkreis mit fünf Transistoren:

Fig. 1.43 Schaltkreis eines AND-Gatters#

Logikgatter#

Um zwei Bits zu addieren, kann z.B. folgende einfache Verschaltung eines UND- und eines ODER-Gatters verwendet werden. Dies entspricht dem sogenannten Halbaddierer.

Fig. 1.44 UND-Gatter# |

Fig. 1.45 ODER-Gatter# |

Fig. 1.46 Halbaddierer# |

||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

Die Addition und natürlich andere Operationen von längeren Zahlen werden in entsprechend komplexeren Schaltungen realisiert.

Mooresches-Gesetz#

Mikrochip |

Anzahl der Transistoren |

Technologieknoten |

Entwicklungsjahr |

|---|---|---|---|

Intel 4004 |

2.300 |

10000 nm |

1971 |

Intel Pentium (P5) |

3.100.000 |

800 nm |

1993 |

Intel Core 2 (Yorkfield) pro Die |

410.000.000 |

45 nm |

2007 |

Intel Itanium 2 Tukwila |

2.046.000.000 |

65 nm |

2010 |

AMD Tahiti XT |

4.312.711.873 |

28 nm |

2011 |

Nvidia Kepler GK110 |

7.100.000.000 |

28 nm |

2012 |

AMD Epyc - 32 Kern Prozessor |

19.200.000.000 |

14 nm |

2017 |

Das Mooresche-Gesetzt besagt, dass sich die Anzahl der Transistoren auf integrierten Schaltkreisen in einem festen Zeitraum verdoppelt. Je nach Zählweise sind es 12, 18 oder 24 Monate.

Fig. 1.47 Entwicklung der Anzahl der Transistorzahl, Quelle: Max Roser, Moore’s Law Transistor Count 1971-2018, CC BY-SA 4.0#

Computerarchitektur#

Von-Neumann-Architektur#

Die allgemeinste, prinzipiell immer noch eingesetzte, Computer-Architektur ist die Von-Neumann Architektur.

Fig. 1.48 Von-Neumann-Architektur, Quelle: Lukas Grossar, Von-Neumann Architektur, als gemeinfrei gekennzeichnet#

CPU: Central processing unit, zentrale Prozesseinheit

Steuerlogik: Steuert das Abarbeiten von Instruktionen.

Rechenwerk: Führt arithmetische Operationen aus.

Bussystem: Erlaubt die Kommunikation der einzelnen Komponenten untereinander.

Speicherwerk: Hat zur Aufgabe Daten und Instruktionen zu speichern.

E/A-Werk: Das Eingabe- / Ausgabewerk stellt die Kommunikation mit externen Komponenten zur Verfügung, z.B. Monitor, Festplatte oder Tastatur.

x86 Architektur#

Abgeleitet von der generellen Von-Neumann-Architektur hat sich im privaten Bereich insbesondere die x86-Architektur durchgesetzt. Sie wird seit 1978, vor allem von Intel und AMD, weiterentwickelt.

Generation |

Jahr |

Beispiel |

|---|---|---|

1 |

1978 |

Intel 8086 |

1 |

1982 |

Intel 80286 |

… |

… |

… |

8 |

2003 |

Athlon 64, Opteron |

9 |

2008 |

Intel Core i3/i5/i7, AMD Phenom II |

Andere Architekturen sind z.B. PowerPC (Apple, IBM, Motorola) oder die ARM-Architektur (ARM).

Speichermedien#

Register: extrem schneller Speicher auf dem u.A. das Rechenwerk seine Operationen ausführt.

Cache: extrem schneller Zwischenspeicher, um die Zugriffszeit auf den Hauptspeicher zu beschleunigen.

Arbeitsspeicher / Hauptspeicher: Hier werden die meisten Daten und Anweisungen abgespeichert.

Massenspeicher – SSD: Etwas schneller als eine Festplatte, jedoch mit deutlich kürzeren Zugriffszeiten.

Massenspeicher – Festplatte: Langsamster verbauter Speicher, jedoch mit einem sehr großem Volumen.

Wechselspeicher – CD-ROM / DVD / BD: Leicht austauschbare Speicher, im allgemeinen langsam und nur lesbar nutzbar.

Nur lesbare Speicher werden oft als ROM (read only memory) bezeichnet; (beliebig) beschreibbare Speicher als RAM (random access memory).

Ob Speicherwerte Daten oder Instruktionen darstellen muss die lesende Einheit selbst entscheiden!

Hierarchie des Speichers#

Optimal wäre ein möglichst schneller Speicher. Jedoch steigt der Herstellungspreis mit der Zugriffsgeschwindigkeit, so dass sich die folgende Volumenverteilung etabliert hat. Die verschiedenen Stufen versuchen die langsamen Zugriffszeiten zu puffern. Insbesondere ist für numerische Berechnungen der Cache, welcher selbst in drei Stufen, sogenannte Level, aufgeteilt ist.

Fig. 1.49 Speicherhierarchie#

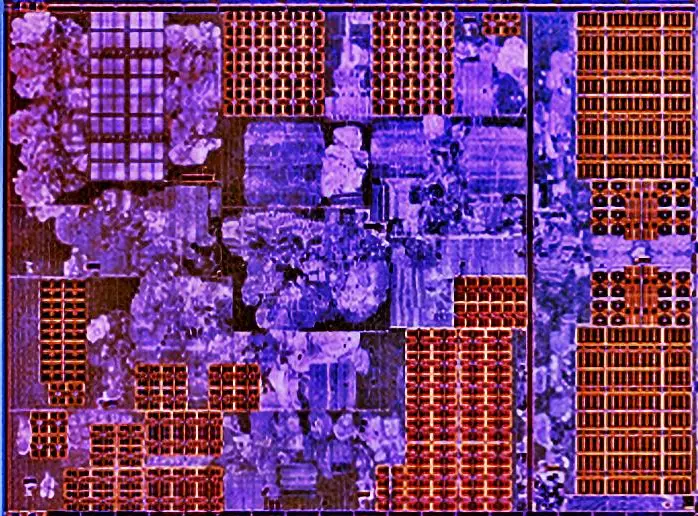

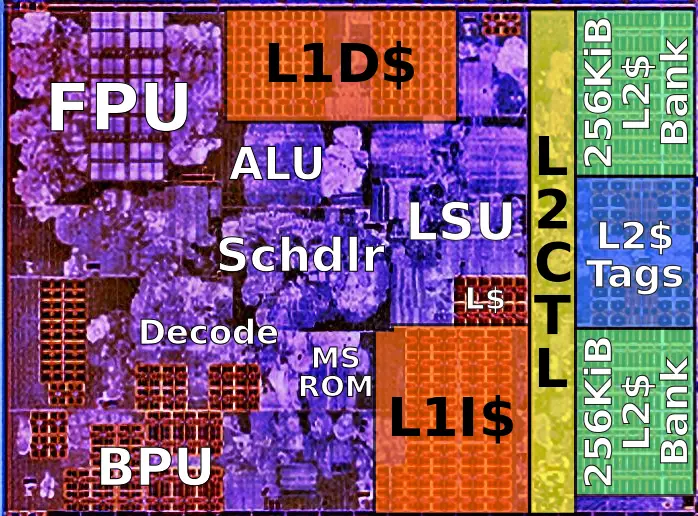

Beispiel AMD Zen Architektur#

Welche Operation als nächstes abgearbeitet wird – und das Veranlassen dieser Operation – wird von der Steuerlogik auf der CPU (central processing unit) geregelt. Daneben befindet sich auf dem Mikrochip auch noch die arithmetische Einheit (Rechenwerk) und der Cache-Speicher, als auch andere Kontrolleinheiten. Diese werden anhand der AMD Zen Architektur exemplarisch vorgestellt.

Zen Core

512 kB L2-Cache

L1 Daten und Instruktions Cache

FPU: Floating Point Unit

ALU: Arithmetic Logic Unit

LSU: Load–store Unit

BPU: Branch Prediction Unit

Fig. 1.50 Aufteilung der Bereiche an einem AMD Zen Core#

Fig. 1.51 Aufteilung der Bereiche an einem AMD Zen Core mit Beschriftung, Quelle Wikichip#

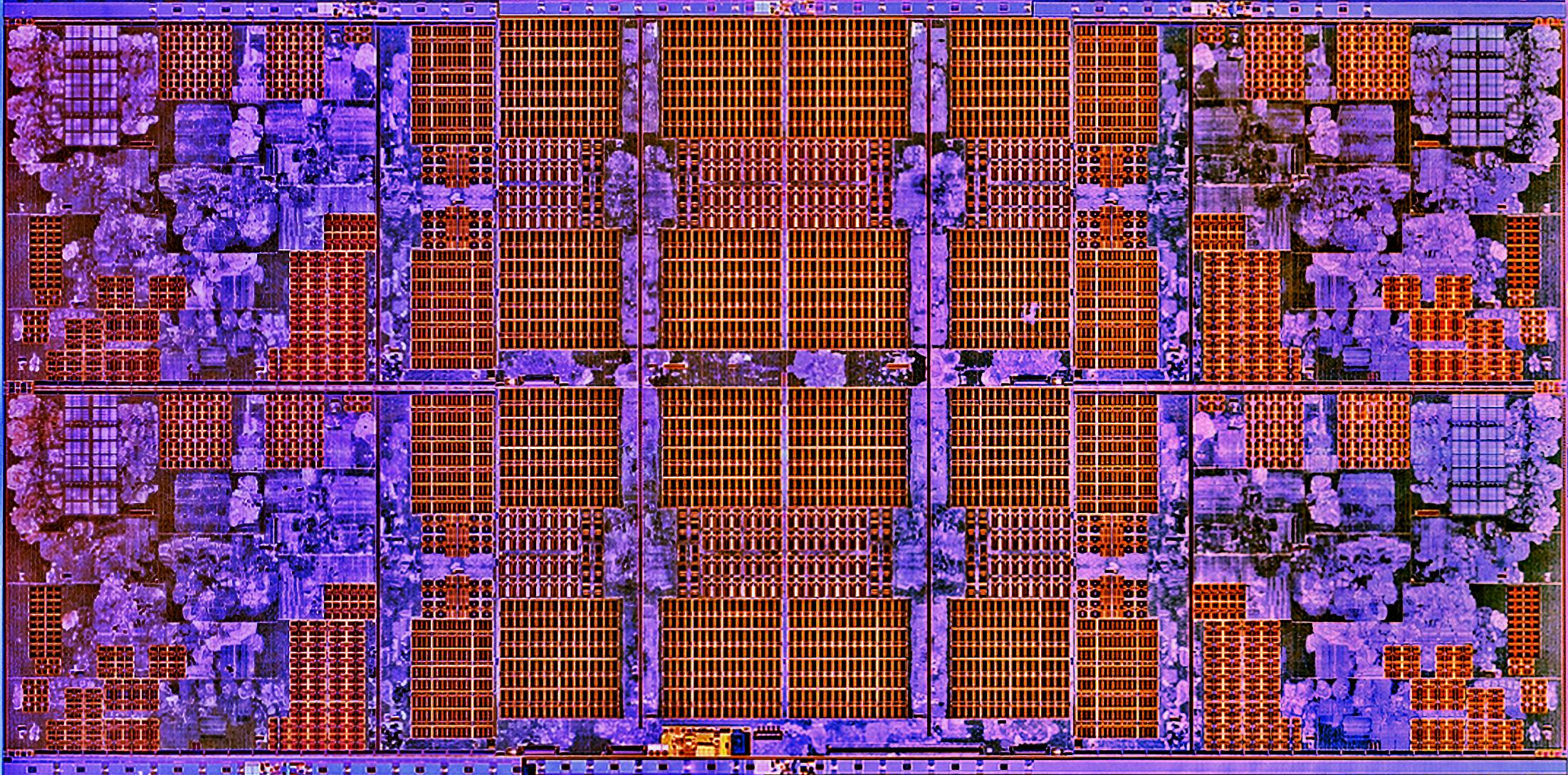

Zen CCX

vier Zen Cores

8 MB L3-Cache

1 400 000 000 Transistoren

Fig. 1.52 Aufteilung der Bereiche an einem AMD Zen CCX#

Fig. 1.53 Aufteilung der Bereiche an einem AMD Zen CCX mit Beschriftung, Quelle Wikichip#

Zen Zeppelin

Zwei Zen CCX

12 Metallschichten

2 km Signalwege

4 800 000 000 Transistoren

22 mm x 9.5 mm Abmessung

Fig. 1.54 Aufteilung der Bereiche an einem AMD Zen Zeppelin#

Fig. 1.55 Aufteilung der Bereiche an einem AMD Zen Zeppelin mit Beschriftung, Quelle Wikichip#

Zen EPYC